基于FPGA的加密算法设计方案详解

随着信息技术和网络化进程的发展,网络通信安全问题日益突出。现场可编程门阵列()以其自身设计灵活、可靠性高的优点广泛应用于加密领域。硬件实现的加密算法不占用计算机资源.加密过程完全与外部总线隔离,具有较高的数据保护能力。算法可灵活改变,具有较强的独立性。加密机由,FPGA和El通信接口组成。FPGA内部算法由VHDL语言编写。该系统适用于要求数据安全较高的场合,其终端可为计算机,银行POS机等,提供数据传输的安全性和保密性。

流密码由密钥和密码算法两部分组成,密钥一般存储在加解密设备内部,在数据传输前已设置完成。密码算法在较长时间内是不变的。在同步流密码中,只要发送端和接收端有相同的密钥和内部状态,就能产生相同的密钥流。

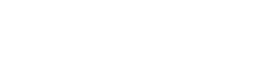

数据传输时,加密端和解密端使用同一个初始密钥,加密时密码流与明文相异或得到密文,同时每隔一定时间加入同步数据;解密时以同步模式产生的密文与密码流进行异或得到明文,同步模式采用63位Gold码。整个加解密过程与发送数据格式如图1所示。在发送密文中加入初始同步码,接收端利用Gold码的三值特性检测Gold码实现同步数据。对接收数据流和Gold码做互相关运算,相关结果满足Gold码的三值特性,说明当前数据流是发送端加入的同步Gold码.标志为密文的起始,然后调用解密算法对后续的密文解密,恢复传输的数据。

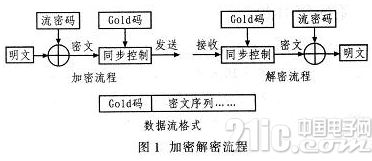

A5/1引是GSM移动通信中数据传输的流密码加密算法。A5/1密码流产生器生成的密码与明文数据帧的每一位相异或得到密文序列。A5/1算法由3个不同长度的线性反馈移位寄存器R1,R2,R3组成,其长度分别为19,22,23位,其反馈特征方程分别为:x18+x17+x16+x13+1,x22+x21+x20+x7+1。算法的初始密钥是64位向量。密码流输出位为3个移位寄存器的异或输出。移位寄存器的使能由多数函数控制。Rl的第8位、R2的第10位、R3的第10位为多数函数数据输入,它们决定3个移位寄存器的移位状况。在这3个数据位中,如果有两个或两个以上的都为0,多数函数值就为0;如果有两个或两个以上的都为1,多数函数值就为1。多数函数输入的3个数据位中与多数函数值相同,相应的移位寄存器就移位。A5/1的硬件实现原理如图2所示。密码流的产生分两个阶段.第一阶段给寄存器装人64位初始值;第二阶段则根据时钟节拍和使能控制产生密码流。

W7H算法与A5/1算法在结构原理上有相似之处。W7算法由8个类似于A5/1算法硬件结构模块并行组成,每一个模块都包含3个线性反馈移位寄存器和多数函数。不同的是w7算法是128位的初始密钥,线性反馈移位寄存器的长度图2 A5/1算法的硬件实现原理和反馈结构都不同于A5/1算法。3个线性反馈移位寄存器长度分别为38、43、47位。8个并行模块采用同一初始密钥。但反馈结构和多数函数的输入位均各不相同。8个模块的输出组成8位密码流,加密效率更高。各线性移位寄存器由固定数据位通过逻辑与产生1位数据,再将该位数据与最高位输出异或,最后将3个移位寄存器输出再异或输出作为本并行块的密码位输出。由于有8个并行块,最后总的输出8 bit,即1字节。设计时,每隔8个时钟周期输出一次,保证数据速率的一致性。

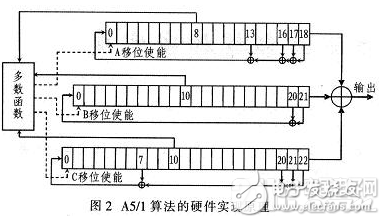

该系统硬件设计由单片机,FPGA和El接121等组成,如图3所示。单片机用于输入用户初始密钥;FPGA负责密钥流产生以及加解密;E1接口实现数据流的发送和接收,完成HDB3码和TTL电平之间的转换,实现通信接口单元和协议数据处理单元之间的全双工通信。

由于通信链路采用E1标准,该系统设计的外部数据链路接121采用E1接口,选用接口器件DS21348。DS21348支持El和T1线接口单元,通过寄存器设置选择E1线可配置为硬件模式,完成HDB3到TTL、TTL到HDB3的电平转换,时钟同步、数据信号格式转换以及数据帧处理。该系统可并行处理两路数据,一路加密,一路解密,实现全双工通信。

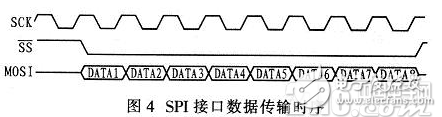

由于TI公司的MSP430系列微处理器平台具有低功耗和小体积等特点,适合便携式应用场合,所以单片机采用MSP430系列,并通过SPI接口实现与FPGA的数据通信。单片机外接一键盘,用于输入初始密钥。考虑到用户输入密钥位数不能很多,可设置简短的密钥,并在单片机内部扩展至算法所需的位数,然后通过单片机SPI接口传送至FGPA。SPI接口共4条信号线:串行时钟(SCK),主机输出/从机输入(MOSI),主机输入/从机输出(MISO),从机片选(SS)。SPI接口可配置为主或从模式。设计配置为主模式。当单片机向FPGA传输命令或数据时,应用SPIO模式。当片选信号丙拉低,在每个时钟(SCK)的上升沿发送数据,无需FPGA向单片机输人数据,所以不使用MISO数据线。片选信号SS与FP-CA的RAM的使能相连,控制数据读入。当用户输人初始密钥后,经过数据扩展,与算法选择数据通过SPI接口传送至FPGA。SPI接口时序如图4所示。

FPGA采用CyeloneII系列中的EP20F256C6,该器件是低成本架构FPGA,可提供多达18 752个逻辑单元.152个用户IO,239 616 bit的存储位,密度超过CyeloneI FPGA的3倍,完全满足系统设计需要。CycloneII FPGA内部的逻辑资源可实现复杂应用。CyeloneII器件采用的低成本串行配置器件,这种串行配置器件最大可提供64 Mbit的nash存储器。所以,采用EP20F256C6可高效完成系统核心算法,有效节约成本。其内部算法由VHDL语言编程实现。主要程序模块:加解密算法模块(A5/1和W7)、数据存储模块、同步产生模块、同步检测模块。加密和解密各有一套独立的模块集合。其中A5/1算法模块的VHDL代码如下:

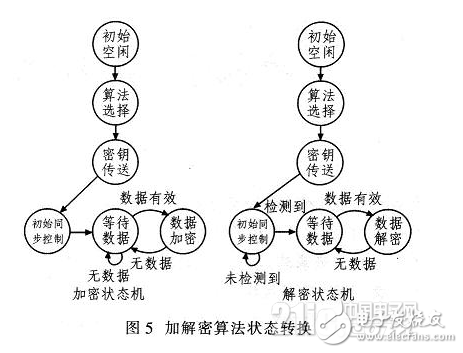

FPGA的模块控制由两个独立的状态机组成,用于处理加密算法和解密算法,其状态转换如图5所示。

系统上电初始化后,由用户向单片机输入初始密钥和算法选择数据,通过SPI接口送入FPGA,FPGA接收到密钥后将初始密钥传给算法模块,算法模块初始化后产生同步Gold码,并等待数据,当待加密数据有效时,启动加密算法;当数据无效时,再次进入等待数据状态。相应地,解密模块先检测起始的同步Gold码,检测到后,当待解密数据有效时,启动解密算法,当待解密数据无效时,再次进入等待数据状态。如此往复,完成数据的加密解密过程。在密钥传输过程中,由于两种算法所需的初始密钥位数不同,当使用w7算法时,初始密钥在送入FPGA中后还需二次扩展达到所需的位数。

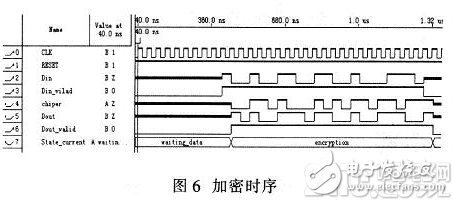

采用QuartuslI 8.0软件仿线 bit的片上存储位,时序分析得到最大工作频率为95.79 MHz。仿线 结论

通过对整个设计的调试验证,结果满足设计要求。整个系统具有较高的安全性和保密性,可为要求通信安全的网络应用提供一种基于硬件的加密方式,基于FPGA的加密算法设计具有很高的灵活性,如果采用更加先进的加密算法,可进一步提高系统的安全性和保密性。

在现代通信和雷达领域中,宽带、高增益、实时并行处理是现代接收机的重要标志。因而,这种具有高速并行处理...

TMP411设备是一个带有内置本地温度传感器的远程温度传感器监视器。远程温度传感器,二极管连接的晶体管通常是低成本,NPN或PNP型晶体管或二极管,是微控制器,微处理器或FPGA的组成部分。 远程精度为1 C适用于多个设备制造商,无需校准。双线串行接口接受SMBus写字节,读字节,发送字节和接收字节命令,以设置报警阈值和读取温度数据。 TMP411器件中包含的功能包括:串联电阻取消,可编程非理想因子,可编程分辨率,可编程阈值限制,用户定义的偏移寄存器,用于最大精度,最小和最大温度监视器,宽远程温度测量范围(高达150C),二极管故障检测和温度警报功能。 TMP411器件采用VSSOP-8和SOIC-8封装。 特性 1C远程二极管传感器 1C本地温度传感器 可编程非理想因素 串联电阻取消 警报功能 系统校准的偏移寄存器 与ADT7461和ADM1032兼容的引脚和寄存器 可编程分辨率:9至12位 可编程阈值限...

TMP468器件是一款使用双线 C兼容接口的多区域高精度低功耗温度传感器。除了本地温度外,还可以同时监控多达八个连接远程二极管的温度区域。聚合系统中的温度测量可通过缩小保护频带提升性能,并且可以降低电路板复杂程度。典型用例为监测服务器和电信设备等复杂系统中不同处理器(如MCU,GPU和FPGA)的温度。该器件将诸如串联电阻抵消,可编程非理想性因子,可编程偏移和可编程温度限值等高级特性完美结合,提供了一套精度和抗扰度更高且稳健耐用的温度监控解决方案。 八个远程通道(以及本地通道)均可独立编程,设定两个在测量位置的相应温度超出对应值时触发的阈值。此外,还可通过可编程迟滞设置避免阈值持续切换。 TMP468器件可提供高测量精度(0.75C)和测量分辨率(0.0 625C)。该器件还支持低电压轨(1.7V至3.6V)和通用双线制接口,采用高空间利用率的小型封装(3mm×3mm或1.6mm×1.6mm),可在计算系统中轻松集成。远程结支持-55C至+ 150C的温度范围。 特性 8通道远程二极管温度传感器精度:0.75&...